#### **Background:**

- $\rightarrow$  Synthesis is tedious and time consuming, especial

- $\rightarrow$  This contrasts with rapid development techniques

- $\rightarrow$  We expect designers productivity to improve with a

## Model:

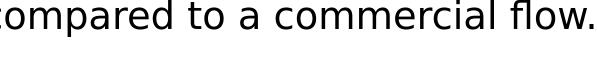

- → LiveSynth targets interactive synthesis with feedb

- $\rightarrow$  LiveSynth allows designers to trigger synthesis mor

- $\rightarrow$  LiveSynth flow is divided into two phases:

- → Interactive step: gives feedback in under a few

- → Background step: high effort optimization, wh

**Fig 1.** LiveSynth shifts the digital design paradigm to incremental changes, allowing for more interations per day.

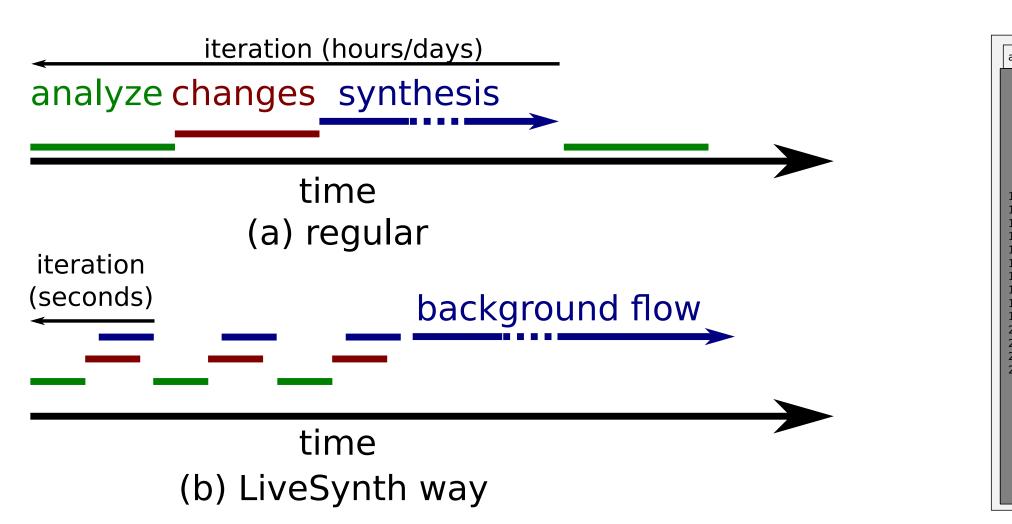

#### **Incremental Flow:**

$\rightarrow$  LiveSynth automatically defines regions of a few the  $\rightarrow$  Invariant cones [1] are regions whose functionality LiveSynth.

$\rightarrow$  During the incremental step, only cones that were

$\rightarrow$  To avoid impact on QoR, if the critical path is hit, the

**Fig 3.** The initial synthesis is performed as usual, and the incremental step is performed when the designer changes the RTL.

# LiveSynth: Towards an Interactive Synthesis Flow

Rafael Trapani Possignolo, Jose Renau Dept. of Computer Engineering University of California, Santa Cruz http://masc.soe.ucsc.edu

| ly during the timing/power closure cycle.<br>popular in software engineering.<br>an interactive synthesis environment.                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                              | Set<br>→ V<br>→ V<br>→ 3<br>→ L                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| back within a few<br>ore frequently and<br>w seconds, with h<br>hen the designer is                                                                                                                                                                                                                                          | incrementally.                                                                                                                                                                                                                                                                                                               | <b>Re</b> :<br>→ 7<br>→ 7                                                                                          |

| <pre>input clk;<br/>input reset;<br/>input [size-1:0] d;<br/>output [size-1:0] q;<br/>output [size-1:0] qb;<br/>reg q;<br/>assign qb = ~q;<br/>alway @(posedge clk or posedge reset)<br/>begin<br/>if(reset) begin<br/>//async reset<br/>q &lt;= 1'b0;<br/>end else begin<br/>q &lt;= d;<br/>end<br/>end<br/>endmodule</pre> | Project info: Messages:   Project name: FPU Errors: 0   Top module: fpu.v Warnings: 2   Target: 32nm Information: 5   Worst negative slack: -0.1 ns Power information:   Worst negative slack: -0.5 ns Newmber of failing endpoints: 5   Neumber of failing endpoints: 5 Switch Leakage Total   Clock 0.50 0.00   Setup Hold |                                                                                                                    |

| As the design<br>new resul                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                              | Micr<br>Arc<br>Sa                                                                                                  |

| do not change du<br>changed are re-sy                                                                                                                                                                                                                                                                                        | t are used as incremental grains.<br>Iring synthesis and are used by<br>Inthesized.<br>Is are also synthesized.                                                                                                                                                                                                              |                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                              | Co<br>→                                                                                                            |

| A A B A B A A A A A A A A A A A A A A A                                                                                                                                                                                                                                                                                      | ementation<br>ementation<br>e boundaries are present over<br>esigns and provide<br>for incremental synthesis.                                                                                                                                                                                                                | Fu<br>$\rightarrow$  <br>$\rightarrow$  <br>$\rightarrow$  <br>$\rightarrow$ F<br>Ac<br>This<br>CNS<br>exp<br>Refe |

|                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                              | [1] D                                                                                                              |

### tup:

We implemented the incremental step of LiveSynth in Ruby. We used an in-house FPU verilog code as benchmark. 32 changes were added in randomly choosen locations, activated through define statements. \_iveSynth was run on-top of a commercial flow and YOSYS [2], an open-source synthesis tool.

#### sults:

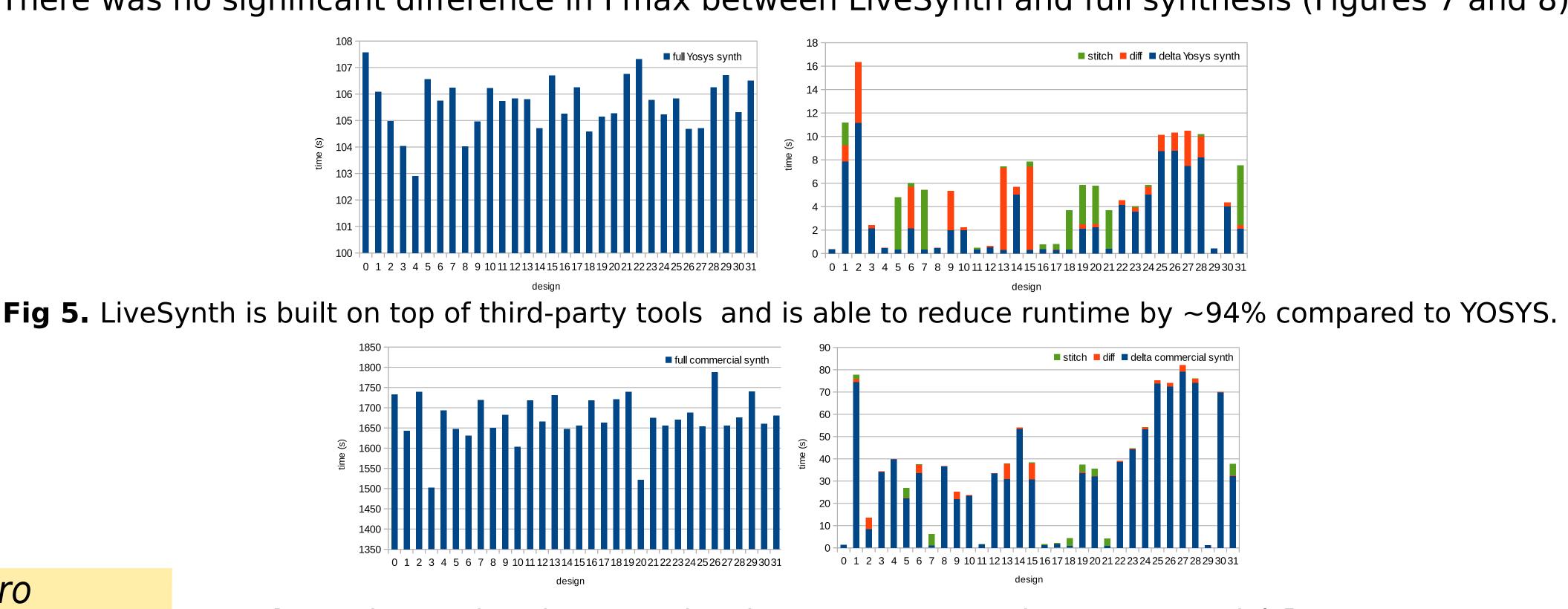

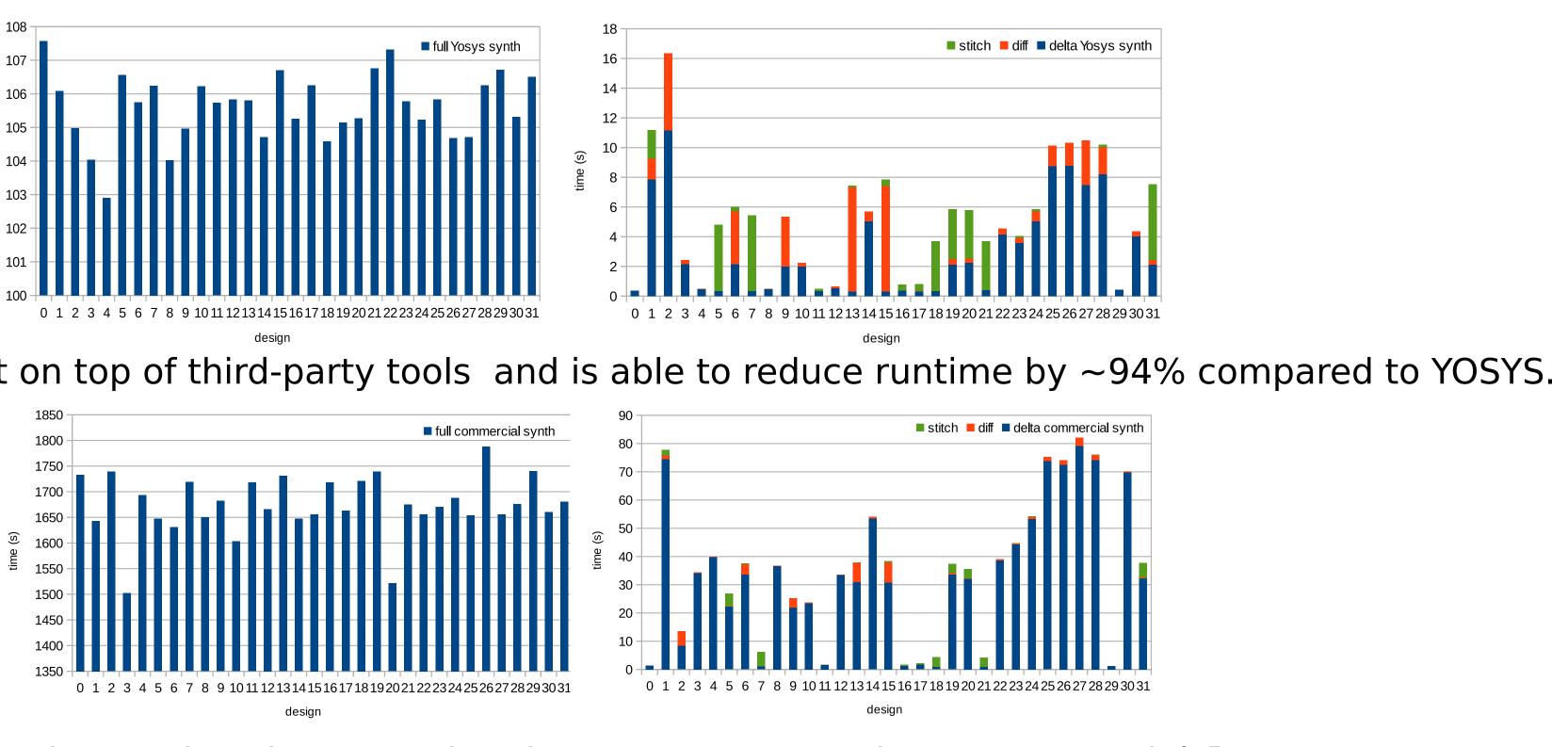

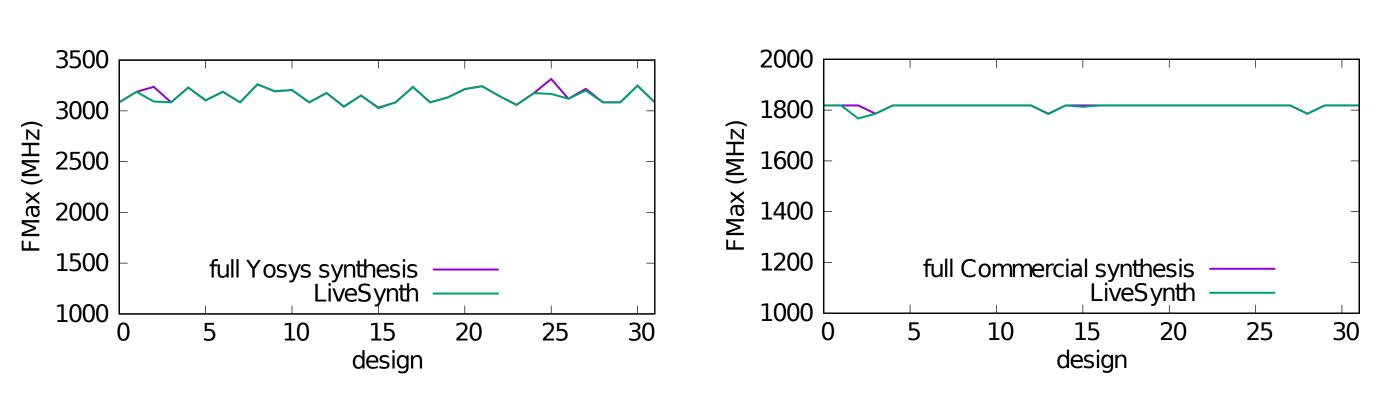

The incremental step of LiveSynth achieves  $\sim$ 95% faster synthesis than a full run (Figures 5 and 6). There was no significant difference in Fmax between LiveSynth and full synthesis (Figures 7 and 8).

chitecture anta Cruz

**Fig 6.** LiveSynth reduces runtime by  $\sim$ 96% compared to a commercial flow.

**Fig 7.** LiveSynth is able to deliver the same QoR as the full synthesis, with minor fluctuations.

#### onclusion:

The incremental step of LiveSynth reduces synthesis time by about 95% for incremental changes. LiveSynth shifts the paradigm to small, incremental changes and more iterations per day. We advocate for an interactive synthesis flow as a way to boost design productivity.

#### iture Work:

Incremental back-end to further improve on feedback accuracy. Improve synthesis to reduce QoR impact.

Further reduce synthesis area to reduce synthesis time in the outliers. FPGA target with further improvement on backend.

#### knowledgments:

is work was supported in part by the National Science Foundation under grants CNS-1059442-003, IS-1318943-001, CCF-1337278, and CCF-1514284. Any opinions, findings, and conclusions or recommendations pressed herein are those of the authors and do not necessarily reflect the views of the NSF.

#### erences:

D. Chen and D. Singh, "Line-level incremental resynthesis techniques for fpgas," in FPGA'11. [2] C. Wolf. Yosys open synthesis suite. http://www.clifford.at/yosys/